|

ЁЁ

4ЁЂЙиМќЕФГЌЯпГЬММЪѕЃЌCore i3ММЪѕНщЩм

Hyper-ThreadingЃЌГЌЯпГЬММЪѕЃК

Hyper-ThreadingЃЌГЌЯпГЬММЪѕ

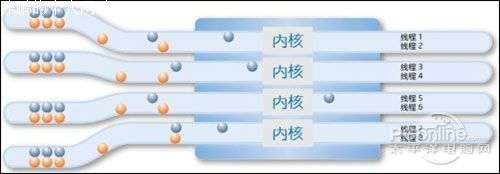

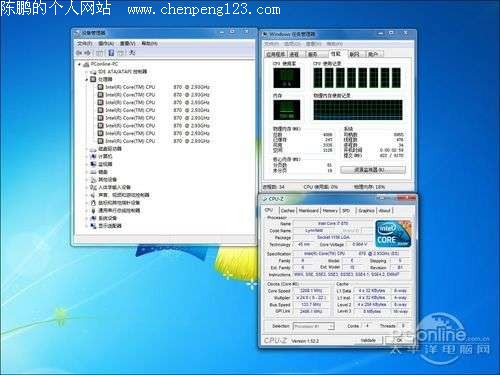

ГЌЯпГЬММЪѕЃЈHyper-ThreadingЃЌМђГЦHTЃЉЃЌзюдчГіЯждк2002ФъЕФPentium 4ЩЯЃЌЫќЪЧРћгУЬиЪтЕФгВМўжИСюЃЌАбСНИіТпМФкКЫФЃФтГЩСНИіЮяРэаОЦЌЃЌШУЕЅИіДІРэЦїЖМФмЪЙгУЯпГЬМЖВЂааМЦЫуЃЌНјЖјМцШнЖрЯпГЬВйзїЯЕЭГКЭШэМўЃЌМѕЩйСЫCPUЕФЯажУЪБМфЃЌЬсИпCPUЕФдЫаааЇТЪЁЃЛљгкNehalemМмЙЙЕФCore i7дйДЮв§ШыГЌЯпГЬММЪѕЃЌЪЙЫФКЫЕФCore i7ПЩЭЌЪБДІРэАЫИіЯпГЬВйзїЃЌДѓЗљдіЧПЦфЖрЯпГЬадФмЁЃ

ГЌЯпГЬММЪѕЪЙCore i7ЫФКЫCPUгЕгаАЫИіТпМФкКЫ

ГЌЯпГЬММЪѕжЛашвЊЯћКФКмаЁЕФКЫаФУцЛ§ДњМлЃЌОЭПЩвддкЖрШЮЮёЕФЧщПіЯТЬсЙЉЯджјЕФадФмЬсЩ§ЃЌБШЦ№ЭъШЋдйЬэМгвЛИіЮяРэКЫаФРДЫЕвЊЛЎЫуЕУЖрЁЃБШЦ№Pentium 4ЕФГЌЯпГЬММЪѕЃЌCore i7ЕФгХЪЦЪЧгаИќДѓЕФЛКДцКЭИќДѓЕФФкДцДјПэЃЌетбљОЭИќФмЙЛгааЇЕФЗЂЛгЖрЯпГЬЕФзїгУЁЃАДееIntelЕФЫЕЗЈЃЌЫФКЫCore i7ЕФHTПЩвддкдіМгКмЩйФмКФЕФЧщПіЯТЃЌШУадФмЬсЩ§20-30%ЁЃЖјжЛгаЫЋКЫаФЕФCore i3ЃЌДюХфHTКѓаЇЙћНЋБШCore i7ИќМгУїЯдЁЃ

ЮЊЮФБОДІРэЬсЫйЃЌЭъећSSE4жИСюЃК

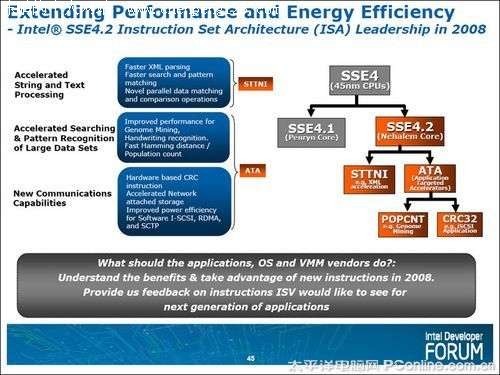

SSE4.1+SSE4.2зщГЩЭъећЕФSSE4ЖрУНЬхжИСю

ЭъећЕФSSE 4(Streaming SIMD Extensions 4ЃЌСїЪНЕЅжИСюЖрЪ§ОнСїРЉеХ)жИСюМЏЙВАќКЌ54ЬѕжИСюЃЌЦфжаЕФ47ЬѕжИСювбдк45nmЕФCore 2ЩЯЪЕЯжЃЌГЦЮЊSSE 4.1ЁЃSSE 4.1жИСюЕФв§ШыЃЌНјвЛВНдіЧПСЫCPUдкЪгЦЕБрТы/НтТыЁЂЭМаЮДІРэвдМАгЮЯЗЕШЖрУНЬхгІгУЩЯЕФадФмЁЃЦфгрЕФ7ЬѕжИСюдкCore i7жавВЕУвдЪЕЯжСЫЃЌГЦЮЊSSE 4.2ЁЃSSE 4.2ЪЧЖдSSE 4.1ЕФВЙГфЃЌжївЊеыЖдЕФЪЧЖдЭјвГЩшМЦЕФXMLЮФБОзжЗћДЎВйзїЁЂДцДЂаЃбщCRC32ДІРэЕШЁЃ

жЕЕУзЂвтЕФЪЧЃЌAMD CPUжЇГжЕФSSE4AКЭIntelЕФSSE4ЪЧВЛЭъШЋЯрЭЌЕФЃЌПЩвдетбљМђЕЅРэНтЃКAMD SSE4AЪЧIntel SSE4ЕФзгМЏЃЌжївЊШЅЕєСЫЮЊIntel 64ЮЛгХЛЏЕФВПЗжЁЃ

Smart CacheжЧФмЛКДцММЪѕЃК

МЬГаNehalemМмЙЙЕФгХЪЦЃЌWestmereМмЙЙЕФCore i3ЭЌбљВЩгУШ§МЖЛКДцЩшМЦЃЌжЇГжSmart CacheжЧФмЛКДцММЪѕЃЌL1КЭL2ЛКДцЮЊФкКЫЛКДцЃЌОпгаГЌЕЭбгГйЃЌЦфжаL1ЛКДцгЩ32KBжИСюЛКДц+32KBЪ§ОнЛКДцзщГЩЁЃУПИіФкКЫ256KBЕФL2ЛКДцЃЈ256KBx 4ЃЉЁЃL3ВЩгУЙВЯэЪНЩшМЦЃЌШнСПЮЊ4MBЃЌБЛЦЌЩЯСНИіКЫаФЙВЯэЃЌвдШЗБЃЫЋКЫдЫЫуЕФаЇТЪзюДѓЛЏЁЃ

МЏГЩЫЋЭЈЕРФкДцПижЦЦїЃК

CPUМЏГЩФкДцПижЦЦїКѓЃЌЮоашЭЈЙ§ББЧХаОЦЌзщРДЗУЮЪФкДцЪ§ОнЃЌМЋДѓГЬЖШЩЯМѕЩйСЫФкДцбгГйЕФЯжЯѓЃЌВЂУїЯдЬсИпФкДцДјПэЃЌЭЌЪБадФмЕУЕНгааЇЬсЩ§ЁЃгыCore i7/i5вЛбљЃЌCore i3ЭЌбљдкМЏГЩСЫФкДцПижЦЦїЃЌЙйЗНжЇГжЫЋЭЈЕРЕФDDR3-1333ФкДцЁЃ

ЩЯвЛвГ [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] ... ЯТвЛвГ >>

|