|

ЁЁ

НјЛЏЕФCPUМмЙЙ аЇТЪДѓЗљЬсИп

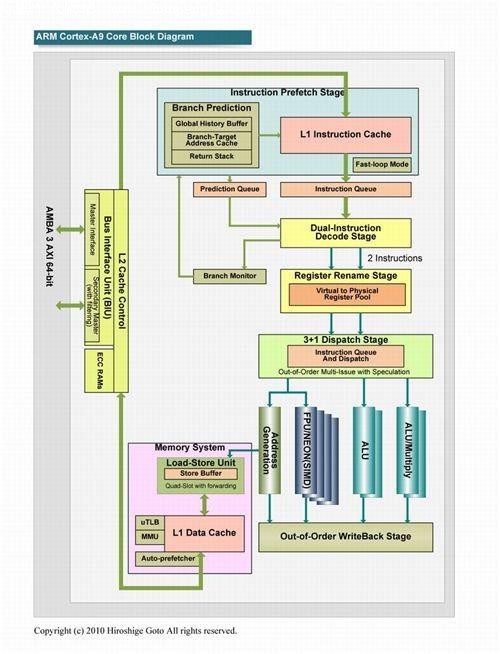

Г§СЫКЫаФЪ§СПЬсЩ§СЫ2БЖЃЌA5 Cortex-A9 CPUМмЙЙвВГіЯжСЫБфЛЏЁЃCortex-A8ВЩгУЕФЪЧЫЋжИСюНтТыЙмЯпЃЌГЬађжИСюВЩгУЕФЪЧIn-OrderжДаа(МДЫГађжДааЃЌжЛФмАДЙЬЖЈЕФгХЯШМЖДІРэЃЌДІРэ ЫйЖШНЯТ§)ЁЃШчЙћвдIntel CPUЖдБШЃЌВюВЛЖрЯрЕБгкЦфPentiumЪБДњВњЦЗЁЃЖјCortex-A9ЫфШЛЭЌбљВЩгУЕФЪЧЫЋжИСюНтТыЃЌЕЋЪЧЦфжИСюжДааЫГађЮЊOut-of- Order(ТвађжДааЃЌПЩвдЖрШЮЮёВЂаажДааЃЌзюДѓЯоЖШЗЂЛгДІРэЦїЕФаЇФмЃЌДІРэЫйЖШПь)ЃЌШнаэСПЗНУцЯрВю25%ЁЃ

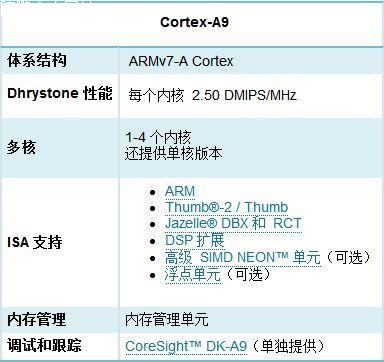

Cortex-A9СїГЬЭМ

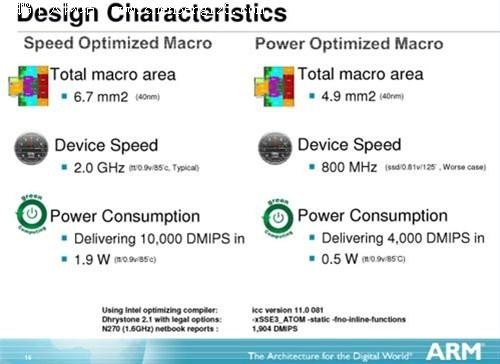

етИіЫљДјРДЕФгАЯьГЬађЃЌПЩвдЭЈЙ§Cortex-A9ЫљеМОнЕФКЫаФЧјгђРДСЫНтЁЃЭЈЙ§ARMЙЋЫОдкШЅФъ(2010Фъ)ЕФЁАCMP ConferenceЁБЫљНјааЕФбнЪОЃЌдкЪЙгУЬЈЛ§Еч 40nmЙЄвеЕФЫЋКЫаФCortex-A9ЕФКЫаФУцЛ§дМдк6.7ЦНЗНКСУзЃЌЦфЦЕТЪФПБъЮЊ2GHzЃЌ1.9WЙІКФЃЌетРяЛЙАќРЈСЫL1ЛКДцКЭзмЯпНгПкЁЃ

ЫГБуНщЩмвЛЯТЕФЪЧX86МмЙЙЫЋжИСюOut-of-Order BobcatКЫаФЛљгк40nmЙЄвеЪБЃЌЕЅКЫаФУцЛ§дк5ЦНЗНКСУзвдЩЯЃЌвђДЫCortex-A9ЫЋКЫвЊБШЫЋКЫЕФX86аОЦЌУцЛ§аЁКмЖрЁЃ

Cortex-A9аТЬиад

вђДЫПЩвдЙРМЦШчЙћВЩгУШ§аЧ45nmЙЄвеЕФЛАЃЌЦфУцЛ§ЛсБШЬЈЛ§Еч40nmвЊДѓЁЃЭЌЪБвд1GHzЦЕТЪЮЊФПБъЕФA5 Cortex-A9КЫаФЃЌЮЊСЫБЃжЄ10аЁЪБЕФајКНЪБМфЃЌЬЈЛ§ЕчвбОФУГізюКУЕФЕчСІПижЦЗНАИСЫЁЃЖјЮвУЧФУЕНЕФiPad2ЕФКЫаФДІРэЦїжїЦЕБЛЫјЖЈдкСЫ 900MHzЃЌПЩМћдкадФмКЭЙІКФЗНУцЯыСНШЋЛЙЪЧЬЋРЇФбСЫЁЃ

ЩЯвЛвГ [1] [2] [3] [4] [5] [6] [7] [8] ЯТвЛвГ

|